DATA SHEET PRELIMINARY VM174D

# General Description

The VM174D is 3 stage Medium-Power Low-Noise amplifier MMIC operating in the frequency range 24 to 30 GHz.

The device has a linear gain of 27 dB and a typical noise figure of 2 dB. Saturated Output RF power is 23 dBm for a biasing current of 120 mA at 4V supply voltage.

It is manufactured with a 100nm pHEMT GaAs process and is especially suited for radar and for telecommunication applications.

## **Typical Features**

Operating frequency range: 24 to 30 GHz

Gain: 27 dB

Noise figure: 2.1 dB

P1dB = 21dBm , Psat= 23dBm

Gain Flatness: +/- 1 dB

Input Return Loss: -10 dB typ.

Output Return Loss: -10 dB typ.

Power supply: 120 mA @  $V_D$ =+4 V,

$V_G = -0.5V$  typ.

• Die Size: 1.2 x 2.4 x 0.1 (mm)

### **Applications**

- Radar

- Test and Measurement

Telecommunications

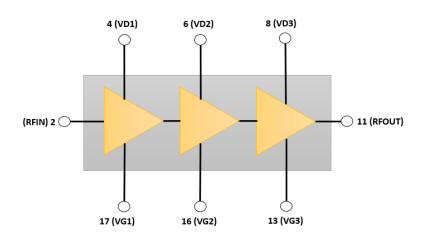

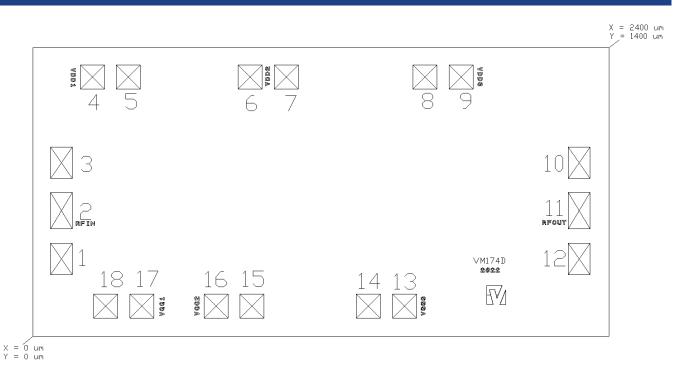

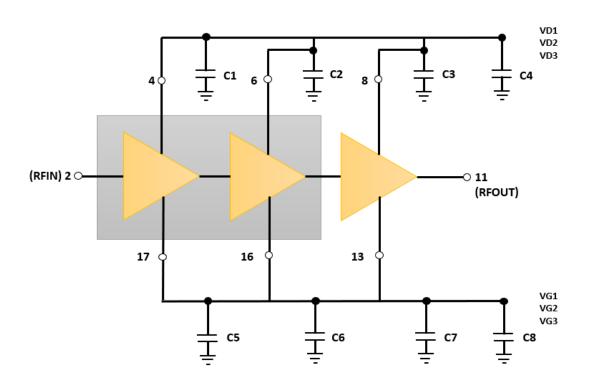

# Functional Block Diagram and Pin Assignment

| Function        | Pin Number |

|-----------------|------------|

| RFIN            | 2          |

| V <sub>D1</sub> | 4          |

| V <sub>D2</sub> | 6          |

| V <sub>D3</sub> | 8          |

| RFOUT           | 11         |

| $V_{G3}$        | 13         |

| $V_{G2}$        | 16         |

| V <sub>G1</sub> | 17         |

VM174D

**PRELIMINARY** DATA SHEET

### **Electrical Specifications**

### Operating conditions unless otherwise noted:

•  $V_D = V_{D1} = V_{D2} = V_{D3} = +4V$

•  $V_G = V_{G1} = V_{G2} = V_{G3} = -0.5V$

$I_D = I_{D1} + I_{D2} + I_{D3} = 120 \text{mA}$ Tamb. = 25 ° C

| Symbol              | Parameter                            | Min  | Тур  | Max  | Unit |

|---------------------|--------------------------------------|------|------|------|------|

| F                   | Frequency range                      | 24   |      | 30   | GHz  |

| G                   | Linear gain                          |      | 27   |      | dB   |

| P1dB                | Output power at 1dB gain compression |      | 21   |      | dBm  |

| Psat                | Output saturated power               |      | 23   |      | dBm  |

| NF                  | Noise Figure                         |      | 2.1  |      | dB   |

| PAE                 | Power Added Efficiency               |      | 28   |      | %    |

| S11                 | Input Return loss                    |      | -10  |      | dB   |

| S22                 | Output Return loss                   |      | -12  |      | dB   |

| V <sub>D1/2/3</sub> | Operating supply voltage             |      | +4   |      | ٧    |

| I <sub>D</sub>      | Supply current                       |      | 120  |      | mA   |

| V <sub>G1/2/3</sub> | Gate voltage                         | -0.6 | -0.5 | -0.4 | ٧    |

### **Absolute Maximum Ratings**

| Symbol         | Parameter             |     | Max  | Unit |

|----------------|-----------------------|-----|------|------|

| V <sub>D</sub> | Drain voltage         |     | +8   | V    |

| I <sub>D</sub> | Supply Current        | 0   | 190  | mA   |

| V <sub>G</sub> | Gate Voltage          | -2  | 0    | V    |

| Pin            | CW Input Power        |     | +10  | dBm  |

| Tst            | Storage temperature   | -55 | +125 | °C   |

| Тор            | Operating temperature | -40 | +85  | °C   |

| Tch            | Channel temperature   |     | +150 | °C   |

Operation of this device above any of these parameters may cause permanent damage.

VM174D

**PRELIMINARY DATA SHEET**

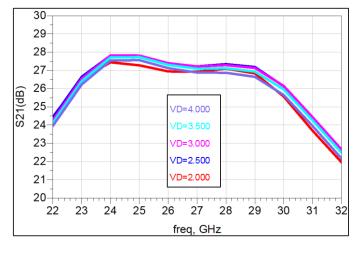

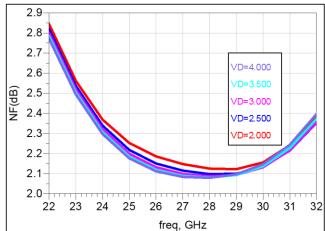

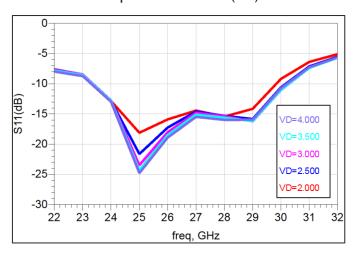

# Typical Performance (Post-layout Simulations)

### Small signal performances vs Supply Drain Voltage

### Operating conditions unless otherwise noted:

- $V_D = V_{D1} = V_{D2} = V_{D3} = +4V$

- $V_G = V_{G1} = V_{G2} = V_{G3} = -0.5V$

- $I_{D} = I_{D1} + I_{D2} + I_{D3} = 120 \text{mA}$ Tamb. = 25 ° C

### Small Signal Gain(dB)

### Noise Figure(dB)

#### Input Return Loss(dB)

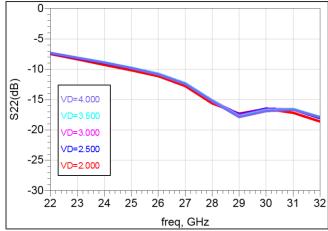

### Output Return Loss(dB)

DATA SHEET PRELIMINARY VM174D

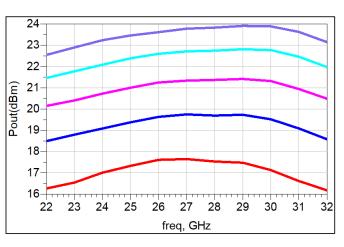

# Typical Performance (Post-layout Simulations)

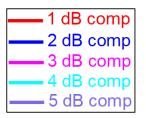

#### Large signal performances vs Gain Compression Level

### Operating conditions unless otherwise noted:

- $V_D = V_{D1} = V_{D2} = V_{D3} = +4V$

- $V_G = V_{G1} = V_{G2} = V_{G3} = -0.5V$

• Tamb.= 25 ° C

### Output Power(dBm)

### Power Added Efficiency(%)

Gain Compression levels

DATA SHEET PRELIMINARY VM174D

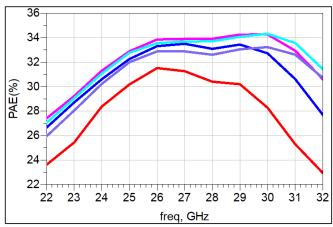

# Typical Performance (Post-layout Simulations)

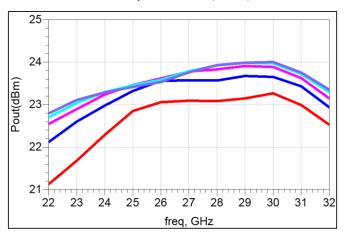

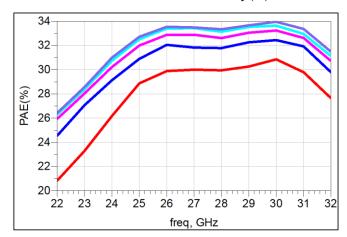

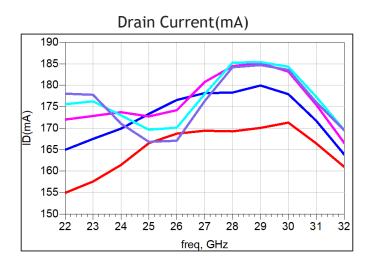

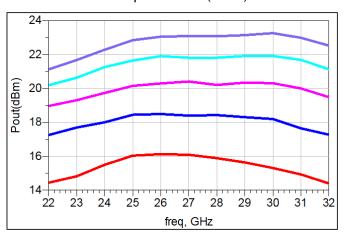

### <u>Large signal performances vs Drain Voltage @ 1dB gain compression</u>

#### Simulation conditions unless otherwise note:

•  $V_D = +2V$  to + 4V,  $V_G = -0.5V$  typ.

• Tamb.= 25 ° C

### Output Power(dBm)

### Power Added Efficiency(%)

#### Drain Current(mA)

VD=4.000 VD=3.500 VD=3.000 VD=2.500 VD=2.000

DATA SHEET PRELIMINARY

VM174D

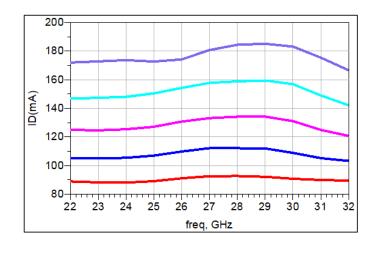

## Typical Performance (Post-layout Simulations)

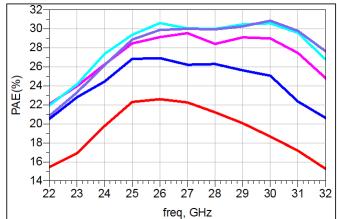

### Large signal performances vs Drain Voltage @ 3dB gain compression

#### Simulation conditions unless otherwise note:

•  $V_D = +2V$  to + 4V,  $V_G = -0.5V$  typ.

• Tamb.= 25 ° C

### Output Power(dBm)

### Power Added Efficiency(%)

### Drain Current(mA)

VD=4.000 VD=3.500 VD=3.000 VD=2.500 VD=2.000

DATA SHEET PRELIMINARY VM174D

# **Pin Description**

| Pin number | Name                           | Description                                                                      | Electrical interface |

|------------|--------------------------------|----------------------------------------------------------------------------------|----------------------|

| 2          | RFIN                           | AC coupled, amplifier input access. Internally matched 50 Ohms.                  | RF IN                |

| 11         | RFOUT                          | AC coupled amplifier output access. Internally matched 50 Ohms.                  | PF OUT               |

| 4, 6, 9    | $V_{D1}$ , $V_{D2}$ , $V_{D3}$ | 1 <sup>st</sup> , 2 <sup>nd</sup> and 3 <sup>rd</sup> stage drain biasing access | V <sub>D1,2,3</sub>  |

| 17, 16, 13 | $V_{G1}$ , $V_{G2}$ , $V_{G3}$ | 1 <sup>st</sup> , 2 <sup>nd</sup> and 3 <sup>rd</sup> stage gate biasing access  | V <sub>G1_2_3</sub>  |

| Die Bottom | GND                            | Die Bottom must be connected to RF and DC Ground                                 | <b>₽</b> GND         |

**DATA SHEET**

# **PRELIMINARY**

VM174D

### Die Layout

### Die Pin Out

|              | Pad cen | ter   | Size Description |       | Description |            | ze Description |  |

|--------------|---------|-------|------------------|-------|-------------|------------|----------------|--|

| Pad Number — | ×(µm)   | y(µm) | μm×μm            | Name  | Value       | Function   |                |  |

| 1            | 119     | 322   | 90×130           | Gnd   |             |            |                |  |

| 2            | 119     | 522   | 90×150           | RFin  | RF in       | RF Input   |                |  |

| 3            | 119     | 722   | 90×130           | Gnd   |             | ·          |                |  |

| 4            | 247     | 1078  | 100×100          | ∨DD1  |             | Drain Bias |                |  |

| 5            | 397     | 1078  | 100×100          | GND   |             |            |                |  |

| 6            | 905     | 1078  | 100×100          | GND   |             |            |                |  |

| 7            | 1055    | 1078  | 100×100          | ∨DD2  |             | Drain Bias |                |  |

| 8            | 1633    | 1078  | 100×100          | GND   |             |            |                |  |

| 9            | 1783    | 1078  | 100×100          | ∨DD3  |             | Drain Bias |                |  |

| 10           | 2276    | 722   | 90×130           | GND   |             |            |                |  |

| 11           | 2276    | 522   | 90×150           | RFout | RF out      |            |                |  |

| 12           | 2276    | 322   | 90×130           | GND   |             |            |                |  |

| 13           | 1547    | 126   | 100×100          | VGG3  |             | Gate Bias  |                |  |

| 14           | 1397    | 126   | 100×100          | GND   |             |            |                |  |

| 15           | 913     | 126   | 100×100          | GND   |             |            |                |  |

| 16           | 763     | 126   | 100×100          | VGG2  |             | Gate Bias  |                |  |

| 17           | 454     | 126   | 100×100          | ∨GG1  |             | Gate Bias  |                |  |

| 18           | 304     | 126   | 100×100          | GND   |             |            |                |  |

DATA SHEET PRELIVINARY VM174D

### **Application Circuit**

- C1, C2, C3, C5, C6, C7 = 100 pF MIM Capacitor (close to the die)

- C4 & C8 = 1 µF

RFIN and RFOUT: 1 Gold Wire (25µm diameter Au)

# Bias-up procedure

- 1. Set  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  to -1V,

- 2. Set  $V_{D1}$ ,  $V_{D2}$  and  $V_{D3}$  to +4V,

- 3. Increase  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  to obtain  $I_D$ =120mA ( $V_G$ =-0.5V Typ.),

- 4. Turn ON RFIN

# Bias-down procedure

- 1. Turn OFF RFIN

- 2. Decrease  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  to -1V,

- 3. Decrease  $V_{D1}$ ,  $V_{D2}$  and  $V_{D3}$  to 0V,

- 4. Set  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  to 0V.

DATA SHEET PRELIMINARY VM174D

|     | lering | •                  |       |

|-----|--------|--------------------|-------|

|     | OFIDA  | <br>O PINO         | ation |

| Olu | erme   | <br><b>101</b> III | ulion |

|     |        | <br>               |       |

| Product Code | Definition                                              |

|--------------|---------------------------------------------------------|

| VM174D       | 24 to 30 GHz 27dB Medium Power<br>Amplifier in Die form |

### **Associated Material**

| Product Code                                     | Definition      |

|--------------------------------------------------|-----------------|

| Packaged die                                     | Contact factory |

| Die Evaluation Board (die EVB)                   | Contact factory |

| Packaged die Evaluation Board (packaged die EVB) | Contact factory |

| Mechanical files (DXF)                           | Contact factory |

| Measurents files (S2P)                           | Contact factory |

# **Product Compliance Information**

#### Solderability:

Use only AuSn (80/20) solder and limit expo-sure to temperature above 300° C during 3-4 minutes, maximum

# ESD Sensitivy Rating:

Test : Human Body Model (HBM)

Standard : JEDEC Standard JESD22-A114

CAUTION! ESD-Sensitive device

### RoHS-Compliance:

This part is compliant with EU 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment).

This product also has the following attributes:

- Lead Free

- Halogen Free (Chlorine, Bromine)

- Antimony Free

- TBBP-A (C15H12Br402) Free

- PFOS Free

- SVHC Free

### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations, and information about Vectrawave:

.......

#### Vectrawave SA

5, rue Louis de Broglie 22 300 Lannion - FRANCE

#### www.vectrawave.com

Email sales: contact\_sales@vectrawave.com

Tel sales:+33 (0)2 57 63 00 20

Represented by